In digital circuit design, multi cycle paths (MCPs) are vital for managing timing across paths that require multiple cycles to meet setup and hold timing requirements. This article explores the significance of multi-cycle paths in Static Timing Analysis (STA), their architectural aspects, and the use of the SDC command set_multicycle_path to define MCPs in STA. Additionally, it covers the implications of unequal clock periods and explains why correctly applying MCP constraints is crucial for effective timing analysis and optimization.

Understanding Multi-Cycle Paths in STA

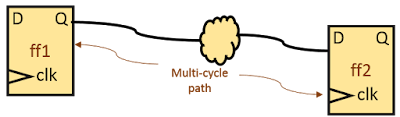

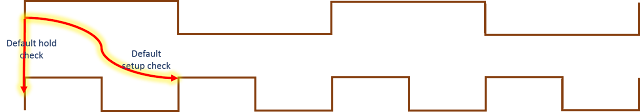

Typically, multi cycle path in STA assumes all timing paths must meet setup and hold checks within a single clock cycle. However, when a path requires multiple cycles, we can specify this with the set_multicycle_path command, which tells the STA engine to time the path over multiple cycles.

Example: Consider a path from ff1/Q to ff2/D, which requires three cycles to complete. By default, multi cycle path in STA would attempt to close timing in one cycle. However, using the command:

set_multicycle_path 3 -setup -from ff1/Q -to ff2/D

this path can be timed across three cycles, updating the setup and hold checks accordingly. The setup check shifts to three cycles, while hold is shifted to two cycles back.

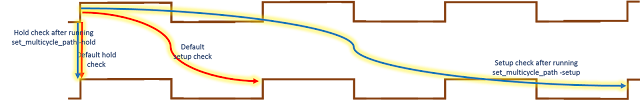

Adjusting Setup and Hold Checks in multi cycle path

Figure: Setup and hold checks before and after applying multicyle for setup-only

In multi-cycle paths, we may only need the hold check to be at the start of the cycle, i.e., zero cycles. To shift the hold check to zero, we use:

set_multicycle_path -hold 2 -from ff1/Q -to ff2/D

This command brings the hold check to zero cycles, which is often needed to prevent excessive timing violations. Here’s a summary:

| Timing Path Setting | Default (Single Cycle) | Multi-Cycle Path (Example) |

| Setup Check | One cycle | Three cycles |

| Hold Check | Same cycle as setup | Zero cycle with MCP applied |

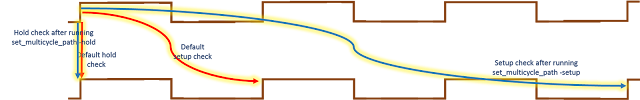

Handling Unequal Clock Periods in Multi Cycle Paths in STA

When the launch and capture clocks have different periods, defining Multi Cycle Paths in STA becomes complex. For example, if the launch clock is slower than the capture clock, the choice of Multi Cycle Paths in STA constraints should consider clock period differences.

Using -start: Applies Multi Cycle Paths in STA cycles based on the launch clock.

set_multicycle_path 2 -setup -from ff1/Q -to ff2/D -start

set_multicycle_path 1 -hold -from ff1/Q -to ff2/D -start

|

| Figure: Setup and hold checks with -start option provided with set_multicycle_path |

Using -end: Applies Multi Cycle Paths in STA cycles based on the capture clock.

set_multicycle_path 2 -setup -from ff1/Q -to ff2/D -end

set_multicycle_path 1 -hold -from ff1/Q -to ff2/D -end

|

| Figure: Setup and hold checks with -end option provided with set_multicycle_path |

Table of Differences in Multi Cycle Paths Application

| Constraint Type | -start Option | -end Option |

| Setup Check Basis | Launch clock period | Capture clock period |

| Hold Check Adjustment | Hold resets to zero cycles | Hold resets to zero cycles |

Single vs. Multi Cycle Paths : Key Differences

| Aspect | Single Cycle Paths | Multi-Cycle Paths |

| Timing Analysis | Checked within a single cycle | Spans multiple cycles |

| Setup and Hold Checks | Default setup and hold checks | Custom checks per MCP requirements |

| Clock Periods | Assumes equal periods | Considers unequal clock periods |

| Design Flexibility | Limited flexibility | Flexible for complex timing needs |

Best Practices for Verifying Multi Cycle Paths and False Paths in STA

Proper verification of multi-cycle paths and false paths can prevent design inefficiencies. Key methods include:

- Simulation-Based Verification: Confirming MCPs through circuit stimulation over multiple cycles.

- Formal Verification: Mathematically validating MCPs against timing constraints.

- Report Generation: Analyzing paths for potential timing issues.

Common Challenges and Best Practices

| Best Practice | Benefit |

| Use Templates | Streamlines Multi Cycle Paths definition |

| Create Checklists | Prevents oversight |

| Follow Guidelines | Aligns with design specifications |

| Collaborate with Teams | Resolves ambiguities early |

| Implement Version Control | Ensures traceability |

Importance of Applying MCPs in Timing Optimization

Incorporating Multi Cycle Paths into timing optimization can significantly improve area, power, and performance:

- Area Optimization: Avoids unnecessary cell sizing.

- Power Optimization: Reduces active power consumption by aligning MCP cycles.

- Enhanced Timing Closure: Minimizes timing pessimism, achieving reliable timing closure.

Conclusion

Multi cycle paths are indispensable for optimizing digital circuit performance in STA. Correctly defined Multi Cycle Paths enable accurate timing analysis and prevent over-constraining the design. The set_multicycle_path command is essential for defining these paths, especially when dealing with unequal clock periods. By adhering to best practices and employing thorough verification, designers can ensure robust and efficient digital circuits with optimal area, power, and timing performance.