Designers use Isolation Cells in VLSI Design as specialized components in VLSI (Very Large Scale Integration) circuits. Synthesis tools insert these cells to separate buses or wires connecting power-gated domains of a circuit to always-on domains. These cells play a crucial role in preventing signals from power-gated areas from corrupting the functionality of always-on sections of the circuit.

Why Do We Need Isolation Cells in VLSI Design?

When a circuit operates in low-power mode, it cuts off the power supply to certain domains. This can lead to uncertain output values (often represented as ‘X’) in those power-gated domains. If these uncertain values propagate to the always-on domain, it can cause malfunctions.

Example: Consider a circuit where components G1 and G2 are in a power-gated domain. When the power turns off, G1 and G2 produce unknown outputs, potentially disrupting the always-on domain. To prevent this, we clamp the values of the wires crossing power domains to either logic 0 or logic 1, depending on the design requirements.

How Do Isolation Cells in VLSI Design Work?

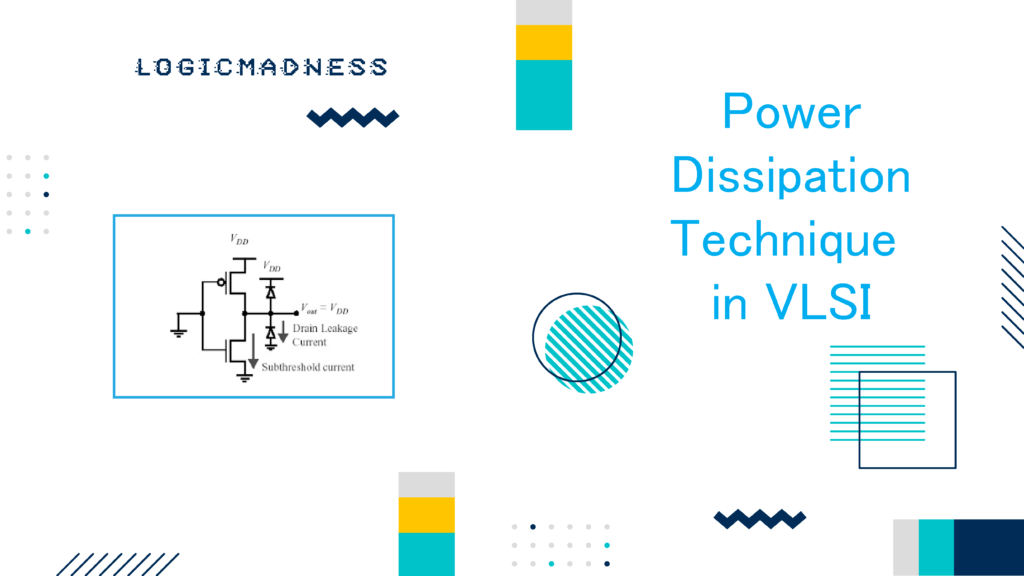

When the synthesis tool clamps a wire to a value of 0, it inserts an AND gate connected to an isolation enable signal from the Power Management Unit (PMU). Conversely, when it clamps a wire to a value of 1, the tool uses an OR gate. These gates, are known as isolation cells. At power cut-off mode ensure that no ‘X’ value affects the always-on domain.

Isolation Cells in VLSI Design Signal Management

- The PMU manages power gating within the design and activates the isolation enable signal before cutting power to prevent ‘X’ values from spreading to the always-on domain.

Key Commands for Isolation Cells in VLSI Design

set_isolation

- This command specifies which elements to isolate and the strategy to use.

- Syntax:

set_isolation isolation_name

- domain domain_name

- isolation power_net net_name | isolation_ground_net net_name | isolation_power_net net_name -isolation_ground_net net_name | no_isolation

- elements list

- clamp_value < 0 | 1 | latch | Z >

- applies_to <inputs | outputs | both>| Argument | Description |

| isolation_name | Name of the isolation strategy defined by the user. |

| domain domain_name | The domain where the strategy will be applied. |

| isolation (type) | Specifies the type of isolation net(s) used. |

| elements list | Ports/nets affected by the isolation strategy. |

| clamp_value | Value to which ports will be clamped (default is 0). |

| applies_to | Whether the strategy applies to inputs, outputs, or both. |

set_isolation_control

- This command defines the control signals for an isolation strategy.

Syntax:

set_isolation_control isolation_name

- domain domain_name

- isolation_signal signal_name

- isolation_sense <high | low>

- isolation <self | parent | sibling | fanout | automatic>| Argument | Description |

| isolation_name | Name of the corresponding isolation strategy. |

| domain domain_name | The domain where the strategy is applied. |

| isolation_signal | Control signal that drives the clamp value. |

| isolation_sense | Indicates if isolation is enabled when the signal is high or low. |

| isolation (type) | Determines where isolation cells are placed in the hierarchy. |

Conclusion

Isolation Cells in VLSI Design are essential for maintaining the integrity of always-on domains in power-gated circuits. By using strategies like clamping and isolation signals, designers can effectively manage power dissipation and prevent unexpected behavior in their VLSI designs.

With the proper implementation of isolation techniques, we can enhance circuit reliability while optimizing power consumption.